### EE 435

#### Lecture 31

String DACs

#### DAC Architectures (Nyquist Rate)

Types

- Voltage Scaling

- Resistor String DACs (string DACs)

- Interpolating

- Current Steering

- Binarily Weighted Resistors

- R-2R Ladders

- Current Source Steering

- Thermometer Coded

- Binary Weighted

- Segmented

- Charge Redistribution

- Switched Capacitor

- Serial

- Algorithmic

- Cyclic or Re-circulating

- Pipelined

- Integrating

- Resistor Switching

- MDACs (multiplying DACs)

#### **DAC** Architectures

Structures

- Hybrid or Segmented

- Mode of Operation

- Current Mode

- Voltage Mode

- Charge Mode

- Self-Calibrating

- Analog Calibration

- Foreground

- Background

- Digital Calibration

- Foreground

- Background

- Dynamic Element Matching

- Laser of Link Trimmed

- Thermometer Coded or Binary

- Radix 2 or non-radix 2

- Inherently Monotone

#### **DAC** Architectures

- Type of Classification may not be unique nor mutually exclusive

- Structure is not mutually exclusive

- All approaches listed are used (and probably some others as well)

- Some are much more popular than others

- Popular Architectures

- Resistor String (interpolating)

- Current Source Steering (with segmentation)

- Many new architectures are possible and some may be much better than the best currently available

- All have perfect performance if parasitic and matching performance are ignored !

- Major challenge is in determining appropriate architecture and managing the parasitics

#### Nonideal Effects of Concern

- Matching

- Parasitic Capacitances (including Charge injection)

- Loading

- Nonlinearities

- Previous code dependence

- Code-dependent settling

- Interconnect resistors

- Noise

- Slow and plagued by jitter

- Temperature Effects

- Aging

- Package stress

#### Observations

- Yield Loss is the major penalty for not appropriately managing parasitics and matching and this loss can be ruthless

- The ultimate performance limit of essentially all DACs is the yield loss associated with parasitics and matching

- Many designers do not have or use good statistical models that accurately predict data converter performance

- If you work of a company that does not have good statistical device models

- Convince model groups of the importantc of dedveloping these models

- (or) develop appropriate test strutures to characterize your process

- Existing nonlinear device models may not sufficiently accurately predict device nonlinearities for high-end data converter applications

#### Observations

- Experienced Designers/Companies often produce superior data converter products

- Essentially all companies have access to the same literature, regularly reverse engineer successful competitors products and key benefits in successful competitors products are generally not locked up in patents

- High-end designs( speed and resolution) may get attention in the peer community but practical moderate performance converters usually make the cash flow

- Area (from a silicon cost viewpoint) is usually not the driving factor in high-end designs where attractive price/mfg cost ratios prevail

### Data Converter Design Strategies

- There are many different DAC and ADC architectures that have been proposed and that are in widespread use today

- Almost all work perfectly if all components are ideal

- Most data converter design work involves identifying the contributors to nonideal performance and finding work-arounds to these problems

- Some architectures are more difficult to find work-arounds than others

- All contributors to nonidealities that are problematic at a given resolution of speed level must be identified and mitigated

- The effects of not identifying nonidealities generally fall into one of two categories

- Matching-critical nonidealities (degrade yield)

- Component nonlinearities (degrade performance even if desired matching is present)

### Data Converter Design Strategies

#### **Remember:**

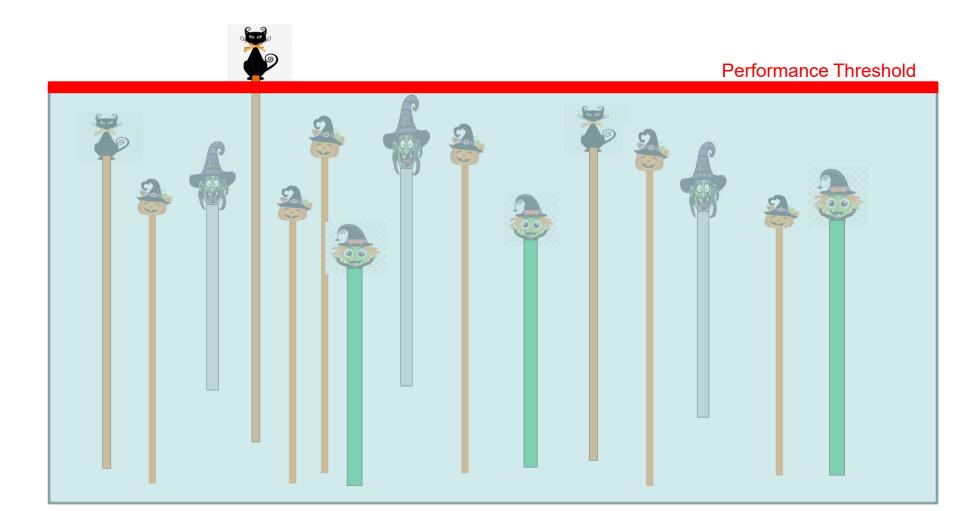

Need to keep nonideal effects below an acceptable performance threshold

Identifying Problems/Challenges and Clever/Viable Solutions

- Many problems occur repeatedly so should recognize when they occur

- Identify clever solutions to basic problems they often are useful in many applications

- Don't make the same mistake twice !

robiem.

The perceived solution:

The practical or clever solution:

Identifying Problems/Challenges and Clever/Viable Solutions

- Many problems occur repeatedly so should recognize when they occur

- Identify clever solutions to basic problems they often are useful in many applications

- Don't make the same mistake twice !

The perceived solution:

The practical or clever solution:

The List ! The List Keeper !

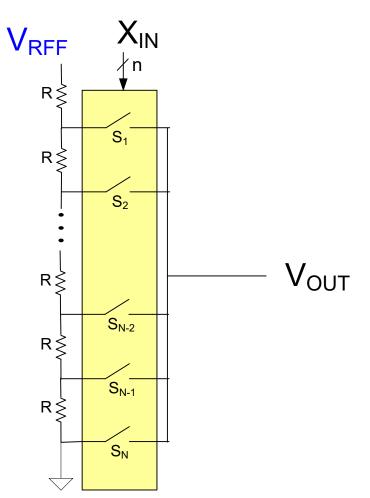

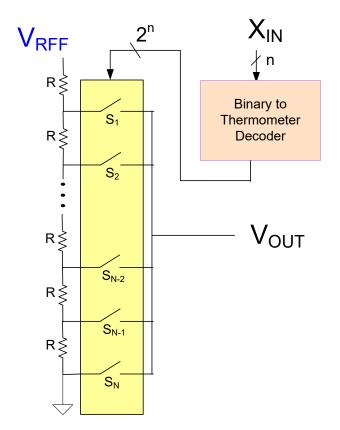

**Basic R-String DAC**

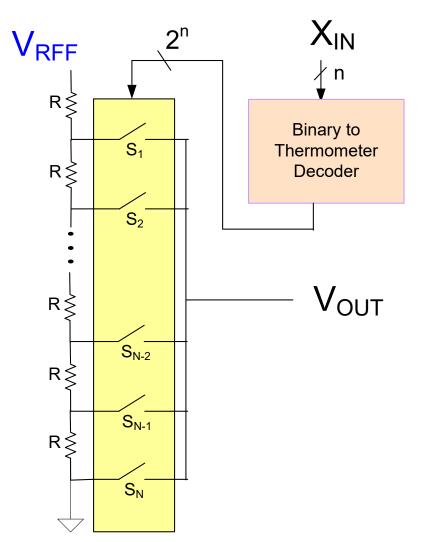

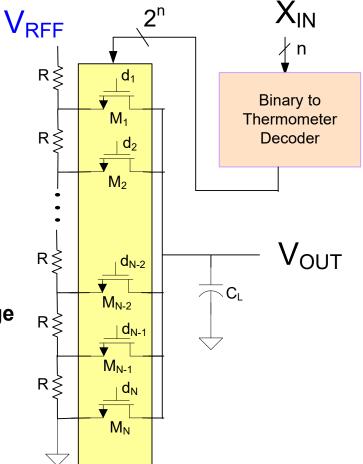

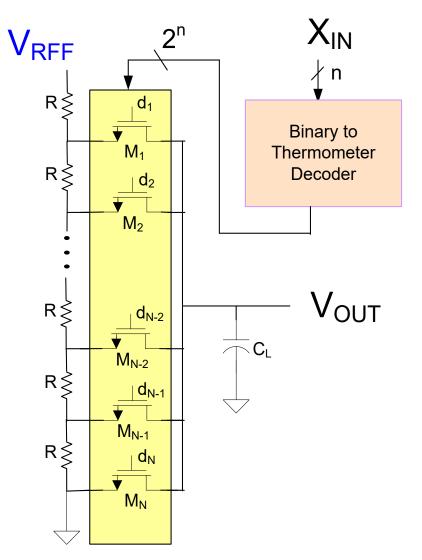

**Basic R-String DAC including Logic to Control Switches**

If all components are ideal, performance of the R-string DAC is that of an ideal DAC!

Key Properties of R-String DAC

- One of the simplest DAC architectures

- R-string DAC is inherently monotone

Possible Limitations or Challenges

If all components are ideal, performance of the R-string DAC is that of an ideal DAC!

#### **Key Properties of R-String DAC**

- One of the simplest DAC architectures

- R-string DAC is inherently monotone

#### **Possible Limitations or Challenges**

- Binary to Thermometer Decoder (BTTD) gets large for n large

- Logic delays in BTTD may degrade performance

- Matching of the resistors may not be perfect

- Local random variations

- Gradient effects

- How can switches be made ?

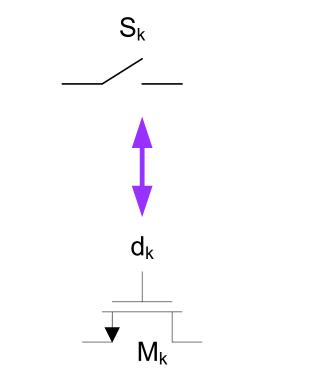

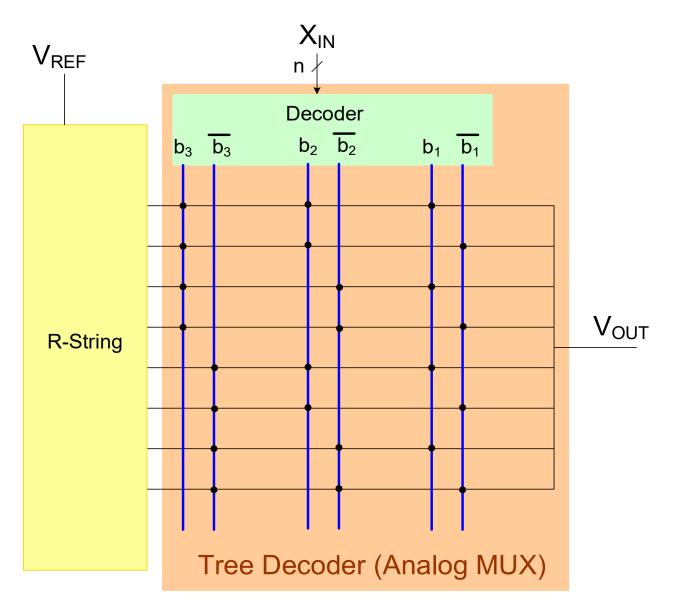

#### Typical strategy for implementing the switch

•Switch array is an analog MUX

Very simple structure

•Switch array combined with the BTTD forms a 2<sup>n</sup>:1 analog MUX

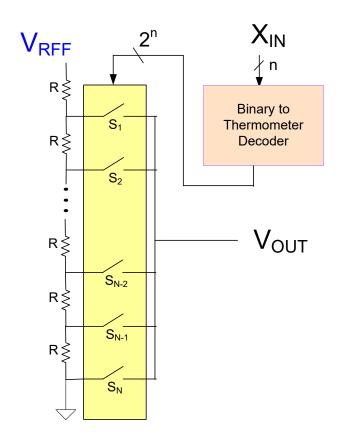

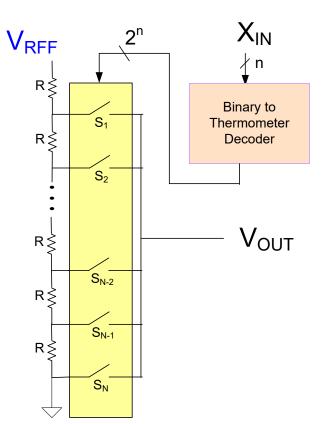

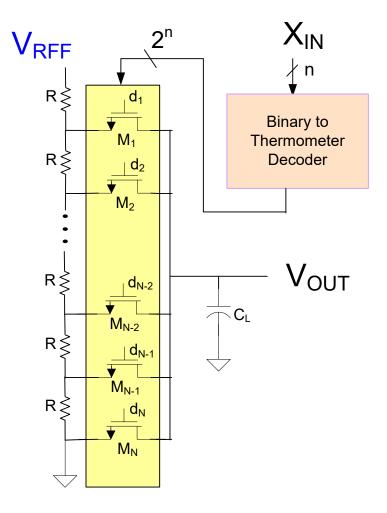

#### **R-String DAC with MOS switches**

**Possible Limitations:**

**R-String DAC with MOS switches**

#### **Possible Limitations:**

Switch impedance is not 0

Switch may not even turn on at all if  $\mathbf{V}_{\text{REF}}$  is large

Switch impedance is input-code dependent

Time constants are input-code dependent

Transition times are previous-code dependent

C<sub>L</sub> has 2<sup>n</sup> diffusion capacitances so can get very large (will discuss this issue next)

Mismatch of resistors local random variation gradient effects

Decoder can get very large for n large

Routing of the 2<sup>n</sup> switch signals can become very long and consume lots of area

## **Basic R-String DAC**

(Review from: EE 330)

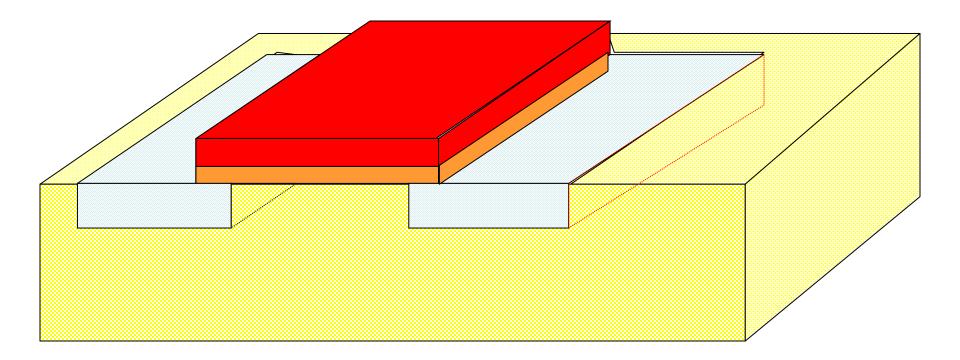

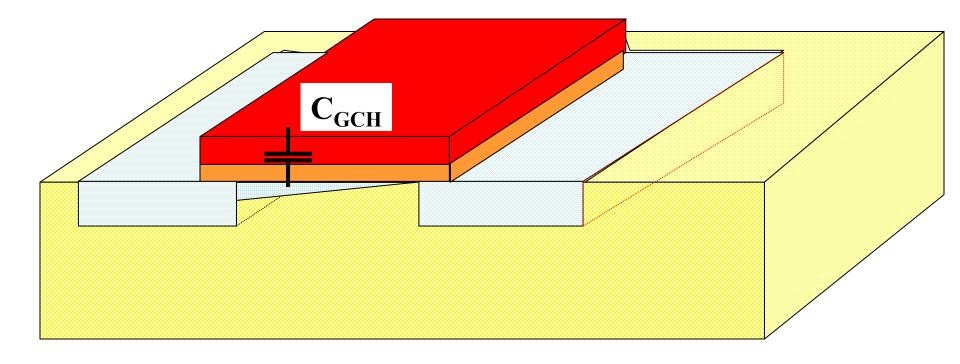

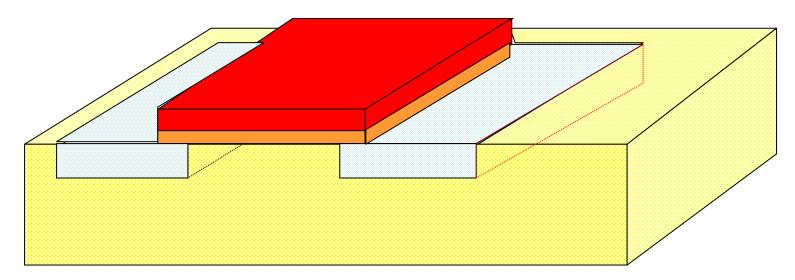

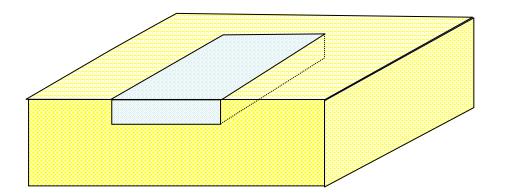

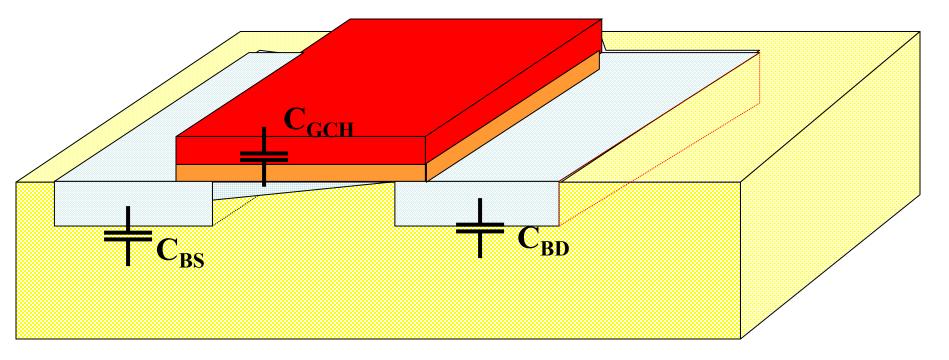

# Parasitic Capacitors in MOSFET

(initially assume saturation and consider two: Gate-channel and diffusion)

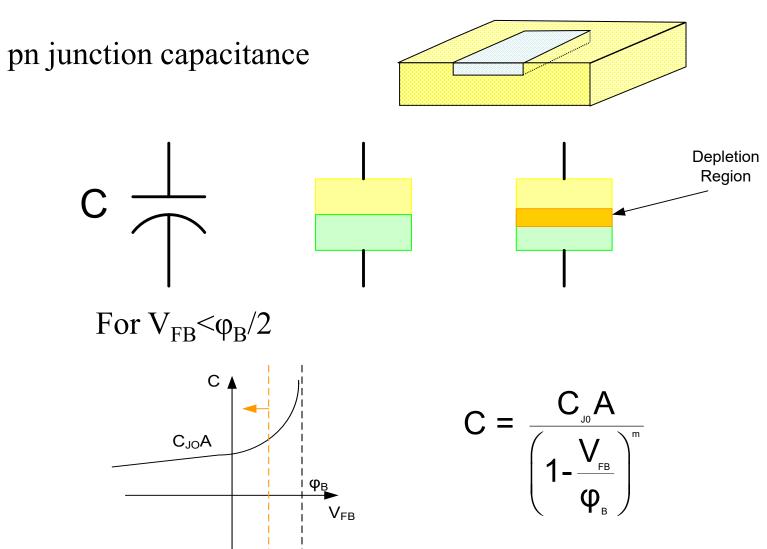

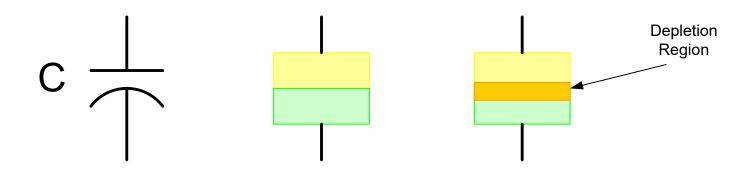

Recall that pn junctions have a depletion region!

pn junction capacitance

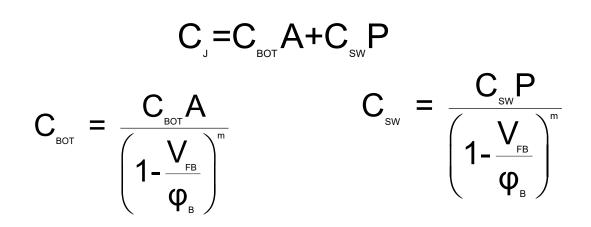

The bottom and the sidewall:

pn junction capacitance

For a pn junction capacitor

(initially assume saturation and consider two: Gate-channel and diffusion)

- Diffusion capacitances nonlinear (dependent upon voltage)

- Many more actually present

- Operating region may affect parasitics

## Question

• Are the parasitic capacitors relevant?

## Observation

Parasitic Capacitors are Small

Consider a minimum-sized transistor

#### Process Parameters from AMI 0.5u Process

| PROCESS PARAMETERS                     | N+ACTV     | P+ACTV | POLY   | PLY2_ | HR POLY2 | MTL1 | MTL2 | UNITS    |       |

|----------------------------------------|------------|--------|--------|-------|----------|------|------|----------|-------|

| Sheet Resistance                       | 81.5       | 101.9  | 21.6   | 1120  | 41       | 0.09 | 0.09 | ohms/sq  |       |

| Contact Resistance                     | 64.6       | 141.9  | 15.8   |       | 26.8     |      | 0.8  | ohms     |       |

| Gate Oxide Thickness                   | 140        |        |        |       |          |      |      | angstrom |       |

| <br>PROCESS PARAMETERS                 | MTL 3      | N\PLY  | N WELL |       |          |      |      |          |       |

| Sheet Resistance                       | 0.06       | 822    | 812    |       |          |      |      | ohms/sq  |       |

| Contact Resistance                     | 0.65       |        |        |       |          |      |      | ohms     |       |

| <br>COMMENTS: N\POLY is N-well under p | alvailiaan |        |        |       |          |      |      |          |       |

|                                        |            |        |        |       |          |      |      |          |       |

| <br>CAPACITANCE PARAMETERS             | N+ACTV     | P+ACTV | POLY   | POLY2 | M1       | M2   | M3   | N_WELL   | UNIT  |

| Area (substrate)                       | 424        | 731    | 07     |       | 32       | 16   | 10   | 39       | aF/un |

| Area (N+active)                        |            |        | 2473   |       | 36       | 16   | 12   |          | aF/un |

| Area (P+active)                        |            |        | 2382   |       |          |      |      |          | aF/un |

| Area (poly)                            |            |        |        | 969   | 56       | 15   | 10   |          | aF/un |

| Area (poly2)                           |            |        |        |       | 50       |      |      |          | aF/un |

| Area (metal1)                          |            |        |        |       |          | 31   | 13   |          | aF/un |

| Area (metal2)                          |            |        |        |       |          |      | 39   |          | aF/un |

| Fringe (substrate)                     | 315        | 247    |        |       | 72       | 58   | 38   |          | aF/un |

| Fringe (poly)                          |            |        |        |       | 57       | 39   | 28   |          | aF/un |

| Fringe (metal1)                        |            |        |        |       |          | 48   | 34   |          | aF/un |

| Fringe (metal2)                        |            |        |        |       |          |      | 55   |          | aF/un |

| Overlap (N+active)                     |            |        | 195    |       |          |      |      |          | aF/un |

|                                        |            |        | 239    |       |          |      |      |          | aF/un |

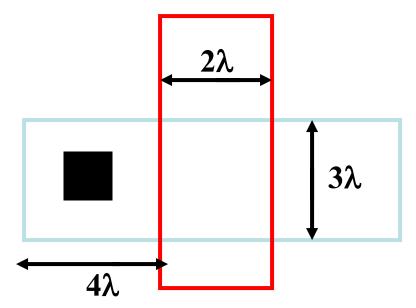

Gate-Channel Capacitance =  $6\lambda^2 \ge 2.47 \text{fF}/\mu^2 = 1.33 \text{fF}$

#### Source Diffusion-Substrate Capacitance = $12\lambda^2 \times .424 \text{fF}/\mu^2 + 14\lambda \times .315 \text{fF}/\mu =$ .46 fF + 1.32 fF = 1.78 fF

Note Sidewall Capacitance larger than Bottom Capacitance

Are these negligible?

#### Are these negligible?

These small capacitors play the dominant role in the speed limitations of most digital circuits

These small capacitors play a major role in the performance of many linear circuits

It is essential that these capacitors (parasitic capacitors) be considered and managed when designing most integrated circuits today!

## Stay Safe and Stay Healthy !

### End of Lecture 31